Содержание страницы

- 1. Физика процесса: Проблема стандартного IGBT

- 2. Решение: Барьерный слой CS (Carrier Stored)

- 3. Анализ структур SPT+ и CSTBT

- 4. Сравнительный анализ и преимущества

- 5. Преимущества и недостатки технологии

- 6. Интересные факты о CSTBT и силовых полупроводниках

- 7. FAQ: Часто задаваемые вопросы (Студенту на заметку)

- Заключение

Что такое CSTBT и SPT+?

1. Физика процесса: Проблема стандартного IGBT

Чтобы понять гениальность решения CSTBT/SPT+, нужно разобраться, как работает классический IGBT. Это гибрид полевого транзистора (MOSFET) на входе и биполярного (BJT) на выходе.

В стандартной структуре, когда транзистор открыт, ток течет от коллектора к эмиттеру. Внутри кристалла это обеспечивается встречным потоком электронов и дырок. Концентрация этой электронно-дырочной плазмы определяет проводимость.

У классического IGBT (Non-Punch Through или ранних Trench версий) распределение плазмы неравномерно. У коллектора (анода) концентрация носителей высока, но по мере приближения к эмиттеру (катоду) она резко падает, так как дырки «высасываются» эмиттерным переходом.

Проблема: Низкая концентрация носителей у эмиттера создает область высокого сопротивления. Это увеличивает напряжение насыщения \( V_{CE(sat)} \) — главный параметр потерь.

2. Решение: Барьерный слой CS (Carrier Stored)

Инженеры задались вопросом: как заставить дырки оставаться в базе дольше, повышая плотность плазмы именно в той зоне, где её не хватает (у эмиттера/затвора)? Ответ был найден в интеграции дополнительного слоя.

Представьте реку (поток дырок), текущую по руслу (база транзистора) к водопаду (эмиттер). В обычном транзисторе вода быстро падает вниз, и уровень воды перед обрывом низкий (низкая проводимость).

Технология CSTBT/SPT+ строит перед водопадом небольшую плотину (слой n-типа с повышенным легированием). Эта плотина не останавливает реку полностью, но заставляет уровень воды перед ней подняться. Воды (носителей заряда) становится больше, русло заполняется целиком, и пропускная способность реки увеличивается.

Техническая реализация

В IGBT с обычной структурой наиболее интенсивный захват (экстракция) дырок происходит из так называемой «подзатворной» части базового слоя. Эта область непосредственно контактирует с обратно смещенным коллекторным переходом внутреннего паразитного p—n—p-транзистора (в терминах эквивалентной схемы IGBT, эмиттер прибора является коллектором внутреннего PNP).

Для повышения плотности носителей заряда в базе, в структуру кристаллов пятого поколения интегрирован дополнительный слой с электронным типом проводимости (CS-слой). Он отделяет область p-кармана (тела) от дрейфового \( n^- \)-слоя.

Ключевые особенности этого слоя:

- Уровень легирования: Концентрация доноров в этом n-слое выше, чем в основной базе (\( N_{CS} > N_{Base} \)).

- Потенциальный барьер: Разница в концентрациях создает локальное электрическое поле, формирующее потенциальный барьер \( \Delta \varphi \) для дырок.

\[ \psi_b = \frac{kT}{q} \ln \left( \frac{N_{CS}}{N_{Base}} \right) \]

Где:

- \( k \) — постоянная Больцмана,

- \( T \) — температура,

- \( q \) — заряд электрона,

- \( N_{CS} \) — концентрация примеси в слое накопления,

- \( N_{Base} \) — концентрация примеси в дрейфовой области.

В результате большая часть дырок, двигаясь от коллектора к эмиттеру, не может сразу преодолеть этот потенциальный барьер. Они скапливаются (аккумулируются) вблизи перехода под затвором. Это приводит к эффекту модуляции проводимости:

Рост концентрации \( p \) (и автоматически \( n \) для сохранения нейтральности) ведет к росту проводимости \( \sigma \), снижая сопротивление базы \( R_{on} \) и, как следствие, напряжение насыщения транзистора \( V_{CE(sat)} \).

3. Анализ структур SPT+ и CSTBT

Данная технология повышения эффективности применена в двух основных конструктивных исполнениях: планарном (SPT+) и траншейном (CSTBT). Рассмотрим их детально.

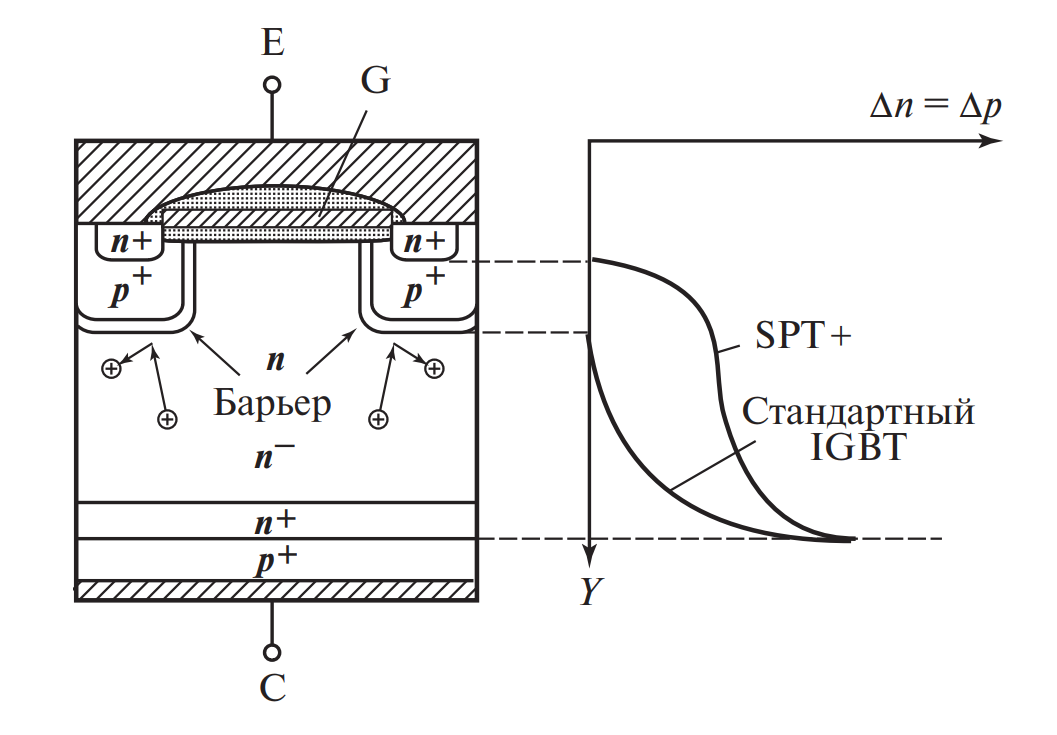

1. Технология SPT+ (Enhanced Planar)

SPT+ (Soft Punch Through Plus) — это эволюция планарной технологии. Здесь затвор расположен на поверхности кристалла.

На схеме показан разрез ячейки. Сверху расположен эмиттерный контакт (E) и затвор (G). Под затвором находится оксидный слой. Ключевой элемент — слой n-типа с повышенным легированием (обозначен как «Барьер n»), который окружает p-области (p-карманы). Этот слой препятствует уходу дырок в p-область эмиттера. Снизу расположена буферная область n+ и коллекторный слой p+.

В структуре SPT+ (см. Рис. 1) мы видим классическую планарную компоновку затвора. Однако вокруг P-карманов (P-well) внедрен дополнительный N-слой.

- Механизм: Этот слой создает барьер для дырок, движущихся снизу вверх.

- Результат: Профиль концентрации носителей становится похож на прямоугольный (равномерный по всей толщине базы), в отличие от треугольного в старых IGBT.

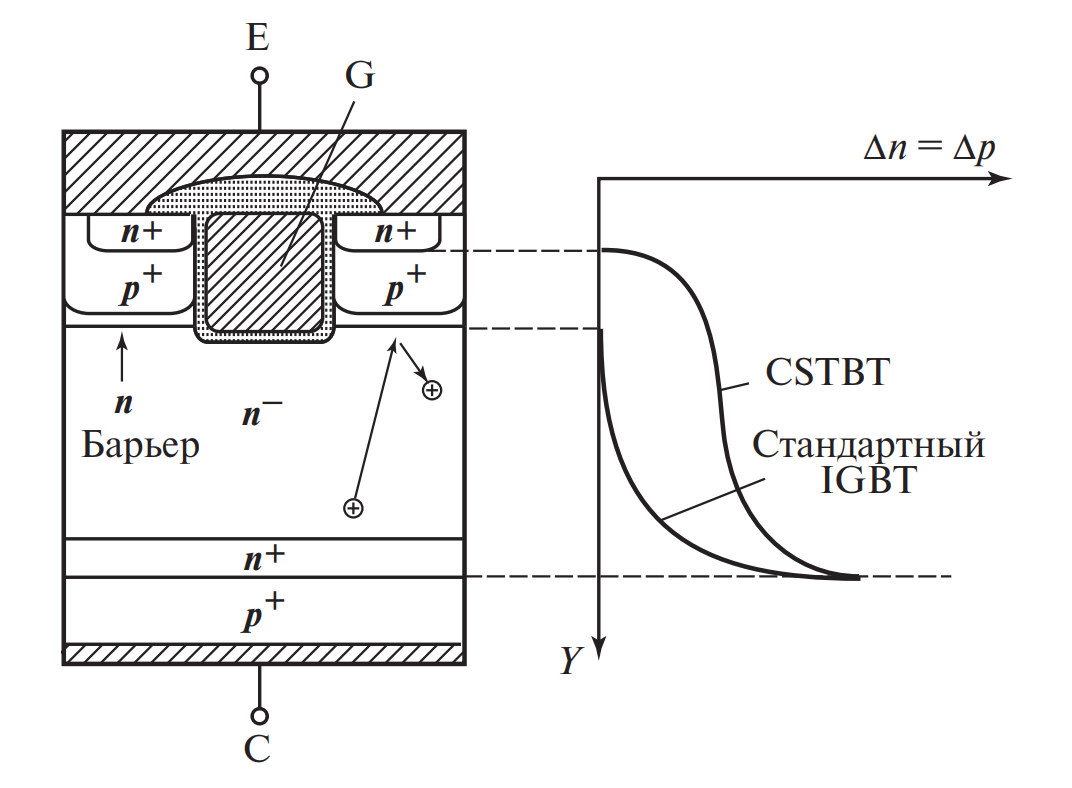

2. Технология CSTBT (Trench Gate)

CSTBT (Carrier Stored Trench Gate IGBT) объединяет в себе преимущества траншейного затвора (Trench) и слоя накопления носителей.

Показана вертикальная структура с траншейным затвором (Trench Gate), утопленным в кристалл. Слой накопления заряда (CS-слой, обозначен как «n-слой») расположен под p-канальной областью, между ячейками затвора. Это создает узкое «горлышко» с потенциальным барьером, эффективно запирающим дырки в дрейфовой области n-.

В CSTBT (см. Рис. 2) используется вертикальная структура затвора. Канавки (траншеи) протравливаются в кремнии, и затвор формируется внутри них вертикально. Это само по себе устраняет паразитное JFET-сопротивление.

Добавление n-слоя (CS-layer) под p-базой в траншейной структуре дает синергетический эффект:

- Траншейная структура обеспечивает высокую плотность каналов.

- Слой CS блокирует выход дырок.

Это позволяет CSTBT достигать рекордно низких значений \( V_{CE(sat)} \), приближаясь к теоретическому пределу для кремния.

4. Сравнительный анализ и преимущества

Внедрение слоя накопления заряда не проходит бесследно для других характеристик. Рассмотрим таблицу сравнения технологий.

| Параметр | Standard NPT/Planar IGBT | SPT+ / CSTBT (Gen 5+) | Влияние на систему |

|---|---|---|---|

| Напряжение насыщения \( V_{CE(sat)} \) | Высокое (2.5В — 3.5В) | Низкое (1.7В — 2.0В) | Снижение статических потерь, меньший нагрев. |

| Плотность тока | Средняя | Высокая | Возможность уменьшить размер кристалла (чипа) при той же мощности. |

| Стойкость к КЗ (SCSOA) | Очень высокая | Высокая (но требует контроля) | Повышенная плотность тока требует более быстрых драйверов защиты. |

| Эффект Миллера | Значительный | Увеличенный (Cres) | Требует более мощных драйверов затвора для подавления осцилляций. |

5. Преимущества и недостатки технологии

Преимущества:

- Сверхнизкие потери проводимости: Благодаря накоплению плазмы у катода, падение напряжения сопоставимо с тиристорами.

- Положительный температурный коэффициент: Облегчает параллельное включение модулей (ток сам выравнивается между чипами).

- Компактность: Более высокая плотность тока позволяет использовать меньшие корпуса.

Недостатки:

- Снижение напряжения пробоя: При неправильном проектировании n-слоя возможно снижение максимального блокируемого напряжения (хотя в серийных моделях это компенсировано).

- Сложность управления КЗ: Высокие токи насыщения означают, что при коротком замыкании через кристалл протекает колоссальная энергия, время до разрушения (t_sc) может быть меньше стандартных 10 мкс.

6. Интересные факты о CSTBT и силовых полупроводниках

- Случайность открытия: Эффект накопления заряда в биполярных приборах изначально считался паразитным, замедляющим выключение, пока инженеры не научились контролировать его для снижения сопротивления.

- Толщина базы: В высоковольтных IGBT (6500В) толщина дрейфовой области может достигать 600-700 микрон, тогда как в низковольтных (600В) CSTBT она тоньше человеческого волоса (менее 60 микрон).

- Траншеи: Ширина траншеи (trench) в современных CSTBT составляет менее 1 микрона, что требует нанотехнологической точности при травлении кремния.

- Температура: Кристаллы CSTBT проектируются для работы при температуре перехода \( T_j \) до 175°C, что на 25-50 градусов выше старых стандартов.

- Золотой стандарт: Технология CSTBT стала де-факто стандартом для инверторов электромобилей (EV), включая Tesla и Toyota Prius, благодаря КПД.

- Легирование нейтронами: Для создания равномерного n-слоя в исходном кремнии часто используют трансмутационное легирование, облучая кремний нейтронами в ядерном реакторе.

- Борьба с «хвостом»: Несмотря на накопление заряда, CSTBT имеют специальные анодные слои (прозрачные эмиттеры), которые позволяют быстро «отсосать» этот заряд при выключении, чтобы избежать длинного «хвостового тока».

7. FAQ: Часто задаваемые вопросы (Студенту на заметку)

Обычный Trench IGBT имеет только геометрическое преимущество (вертикальный канал). CSTBT добавляет к этому физический барьер для дырок, что дополнительно снижает падение напряжения на 20-30% при том же токе.

Потому что в IGBT ток течет через канал MOSFET, который находится под затвором. Дырки стремятся к этой области, чтобы рекомбинировать с электронами или уйти в эмиттер, но барьер CS-слоя их останавливает именно там.

Теоретически, больше заряда = медленнее выключение. Однако современные технологии оптимизируют время жизни носителей так, что выигрыш в напряжении насыщения перевешивает незначительное увеличение потерь переключения.

Чаще всего да, но нужно проверить резисторы затвора (\( R_g \)). Возможно, их придется увеличить, чтобы предотвратить осцилляции, или уменьшить для ускорения.

SPT расшифровывается как Soft Punch Through (Мягкий прокол). Плюс (+) означает наличие дополнительного n-слоя для накопления заряда, аналогичного технологии CSTBT, но в планарном исполнении.

Заключение

Нормативная база

ГОСТ IEC 60747-9-2019 — Приборы полупроводниковые. Часть 9. Транзисторы биполярные с изолированным затвором (IGBT). (Идентичен международному стандарту IEC 60747-9:2019). Это основной документ, регламентирующий терминологию и методы измерений.

ГОСТ IEC 60747-9-2019 — Приборы полупроводниковые. Часть 9. Транзисторы биполярные с изолированным затвором (IGBT). (Идентичен международному стандарту IEC 60747-9:2019). Это основной документ, регламентирующий терминологию и методы измерений.- ГОСТ 20859.1-89 — Приборы полупроводниковые силовые. Термины и определения.

Список рекомендуемой литературы

- Б. Дж. Балига. «Силовые полупроводниковые приборы». Москва, Техносфера, 2010. (Фундаментальная «библия» от создателя IGBT).

- Флоренцев С.Н. «Силовая электроника. Современное состояние и перспективы развития».

- Application Notes (Руководства по применению) от ведущих производителей: Infineon, Semikron, Mitsubishi Electric.